Product Summary

The BS62LV8001EIP55 is a very low power/voltage CMOS SRAM organized as 1,048,576 words by 8 bits and operates from a wide range of 2.4V to 5.5V supply voltage. The BS62LV8001EIP55 provides both high speed and low power features with a typical CMOS standby current of 1.5uA at 3V/25oC and maximum access time of 55ns at 3.0V/85oC. Easy memory expansion is provided by an active LOW chip enable(CE1) , an active HIGH chip enable (CE2) and active LOW output enable (OE) and three-state output drivers. The BS62LV8001EIP55 has an automatic power down feature, reducing the power consumption significantly when chip is deselected. The BS62LV8001EIP55 is available in 48B BGA and 44L TSOP2 packages.

Parametrics

BS62LV8001EIP55 absolute maximum ratings: (1) V TERM Terminal Voltage with Respect to GND: -0.5 to Vcc+0.5 V; (2) T BIAS Temperature Under Bias: -40 to +85 ℃; (3) T STG Storage Temperature: -60 to +150 ℃; (4) P T Power Dissipation: 1.0 W; (5) I OUT DC Output Current: 20 mA.

Features

BS62LV8001EIP55 features: (1) Three state outputs and TTL compatible; (2) Fully static operation; (3) Data retention supply voltage as low as 1.5V; (4) Easy expansion with CE1, CE2 and OE options; (5) High speed access time: 55 55ns, 70 70ns; (6) Automatic power down when chip is deselected; (7) Wide Vcc operation voltage : 2.4V ~ 5.5V.

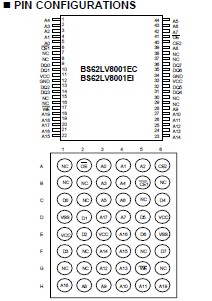

Diagrams

|

BS62LV1023DC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

BS62LV1023DI |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

BS62LV1023JC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

BS62LV1023JI |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

BS62LV1023PC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

BS62LV1023PI |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)